| Stage | Unpipelined | Pipielined |

| IF | IR ← Mem[PC] NPC ← PC + 4 |

IF/ID.IR ← Mem[PC] PC ← PC + 4 IF/ID.NPC ← PC + 4 |

| ID |

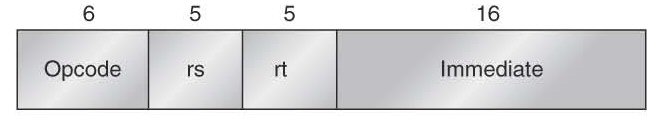

A ← Regs[IR.rs] B ← Regs[IR.rt] Imm ← sign-extended(IR.Immediate) |

ID/EX.A ← Regs[ID/IF.IR.rs] ID/EX.B ← Regs[ID/IF.IR.rt] ID/EX.NPC ← IF/ID.NPC ID/EX.IR ← ID/ID.IR ID/EX.Imm ← sign-extended(IF/ID.IR.Immediate) |

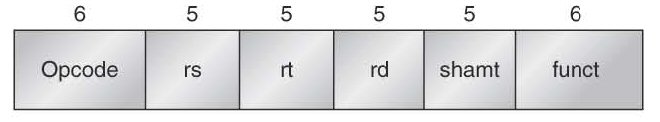

| EX | ALUOutput ← A funct B |

EX/MEM.IR ← ID/EX.IR EX/MEM.ALUOutput ← ID/EX.A funct ID/EX.B |

| MEM | PC ← PC + 4 |

MEM/WB.IR ← EX/MEM.IR MEM/WB.ALUOutput ← EX/MEM.ALUOutput |

| WB | Regs[IR.rd] ← ALUOutput | Regs[MEM/WB.IR.rd] ← MEM/WB.ALUOutput |

| instruction | cycle i | cycle i+1 | cycle i+2 | cycle i+3 | cycle i+4 | cycle i+5 | cycle i+6 | cycle i+7 | cycle i+8 | |

| instruction A (taken branch) | IF | ID | EX | MEM | WB | |||||

| instruction B | IF | ID | EX | MEM | WB | |||||

| instruction C | IF | ID | EX | MEM | WB | |||||

| instruction D | IF | ID | EX | MEM | WB | |||||

| instruction X (branch destination) | IF | ID | EX | MEM | WB |

| instruction | cycle i | cycle i+1 | cycle i+2 | cycle i+3 | cycle i+4 | cycle i+5 | cycle i+6 | |

| instruction A (taken branch) | IF | ID | EX | MEM | WB | |||

| instruction B | IF | ID | EX | MEM | WB | |||

| instruction X (branch destination) | IF | ID | EX | MEM | WB |

LD R1, 45(R2)

DADD R5, R1, R7

LD R1, 45(R2)

DADD R5, R6, R7

DSUB R8, R1 R7